Time Sensitive Networking Switch

🗺 Location: Indian Institute of Science (IISc), Bangalore, India

📅 Duration: March 2021 - August 2024

💰 Funded by: Ministry of Electronics and Information Technology (MeitY), Government of India and Center for Networked Intelligence (CNI), a Cisco CSR initiative.

👩🏫 Guided by: Prof. Chandramani Singh and Prof. TV Prabhakar

Note: This work is under progress. The information in this page is up to August 2022. The application developed over this work is detailed in the project “Designing Tactile Cyber-Physical Systems”.

Objective Link to heading

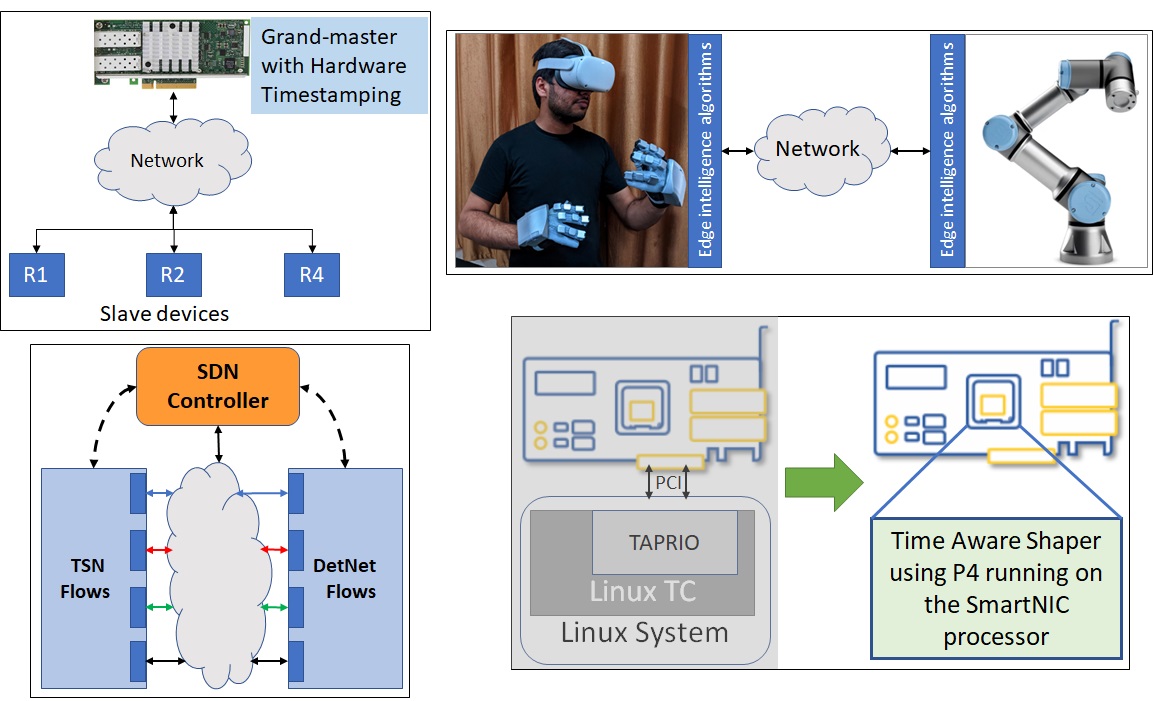

- To develop Time-Senstitive Networking (TSN) enabled ethernet switches on programmable network hardware (Netronome Agilio SmartNIC) using P4 programming language. To implement time synchronization in the network and then set up a TSN network. This involves implementing time aware shaper and gate control list at the switch ports.

- To enable applications requiring ultra-reliable low latency communication (uRLLC) such as remote robotics assisted surgery.

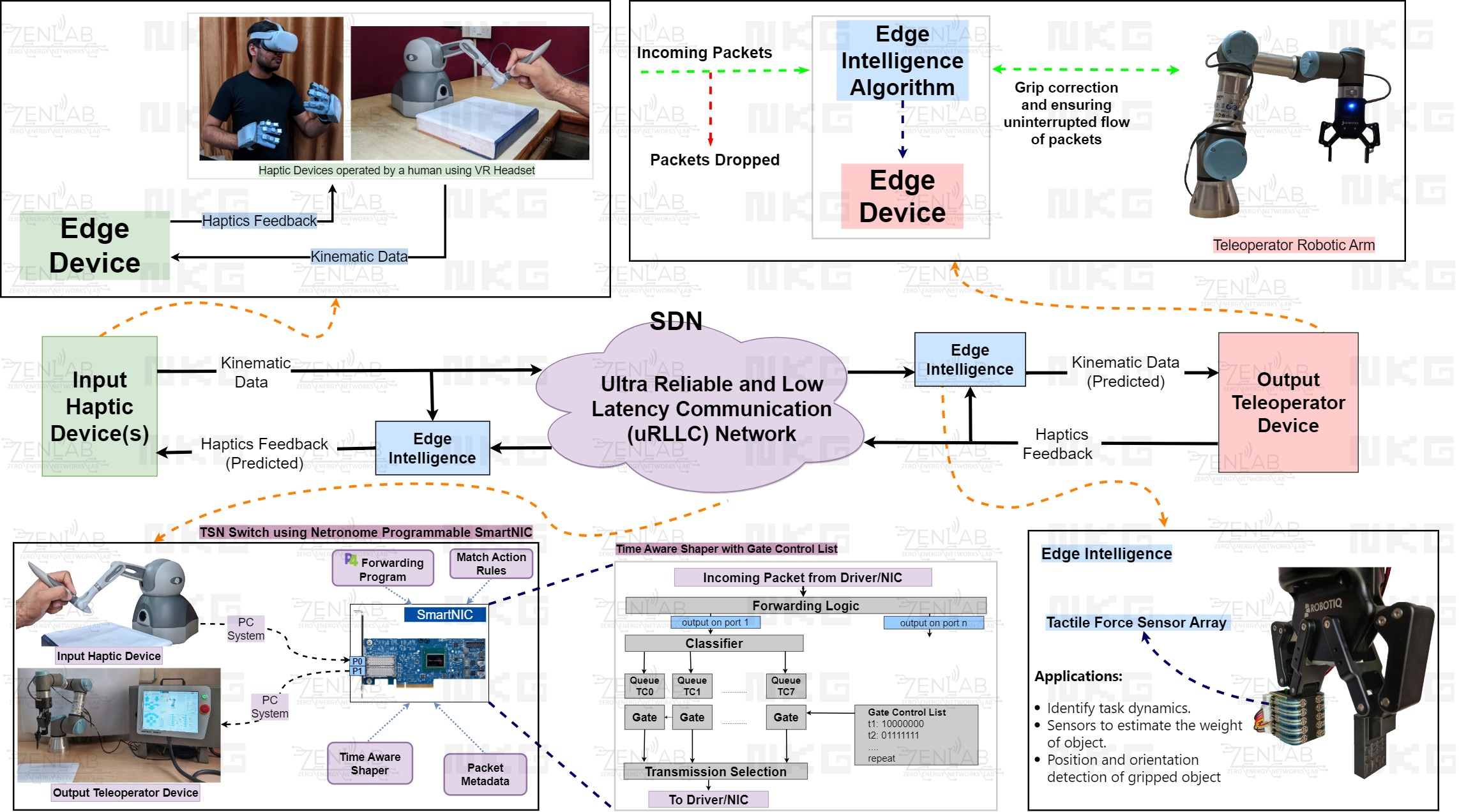

Overview of the project

Modules: Link to heading

Time-Sensitive Networking (TSN) switch (Towards implementing IEEE 802.1 TSN):

- Time Synchronization (Towards implementing IEEE 802.1AS)

- Time Aware Shaper (Towards implementing IEEE 802.1Qbv)

- Packet duplication and Elimination (Towards implementing IEEE. 802.1CB)

- Edge intelligent switch ports on programmable switches using P4

Work Done Link to heading

Time synchronization Link to heading

Implemented Precision Time Protocol (PTP) on Linux devices. Tested using four Raspberry Pi devices – R1, R2, R3, and R4. R3 is the grand-master clock using the Best Master Clock Algorithm (BMCA). The remaining devices are in slave configuration. Using software timestamping a sub 100 μs synchronization error was obtained.

Time synchronization using PTP

P4-based switch using Netronome Agilio SmartNIC Link to heading

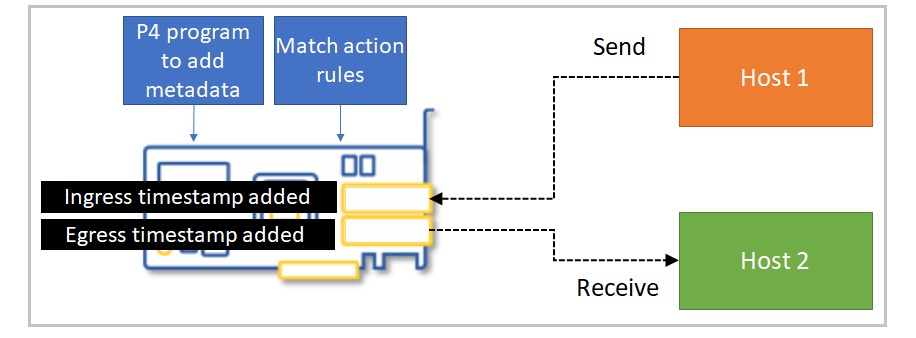

We have set up an ethernet switch using P4 programming language on the Netwronome Agilio SmartNIC. The match action table/rules contain the MAC addresses of the connected hosts. IP address is extracted from the packet and the packet is forwarded to a matching MAC address. The P4 program is also useful for obtaining and adding timestamps in a custom metadata header. Obtaining timestamps at the ports of the switch is a basic step for TSN.

P4 based switch using Netronome Agilio SmartNIC

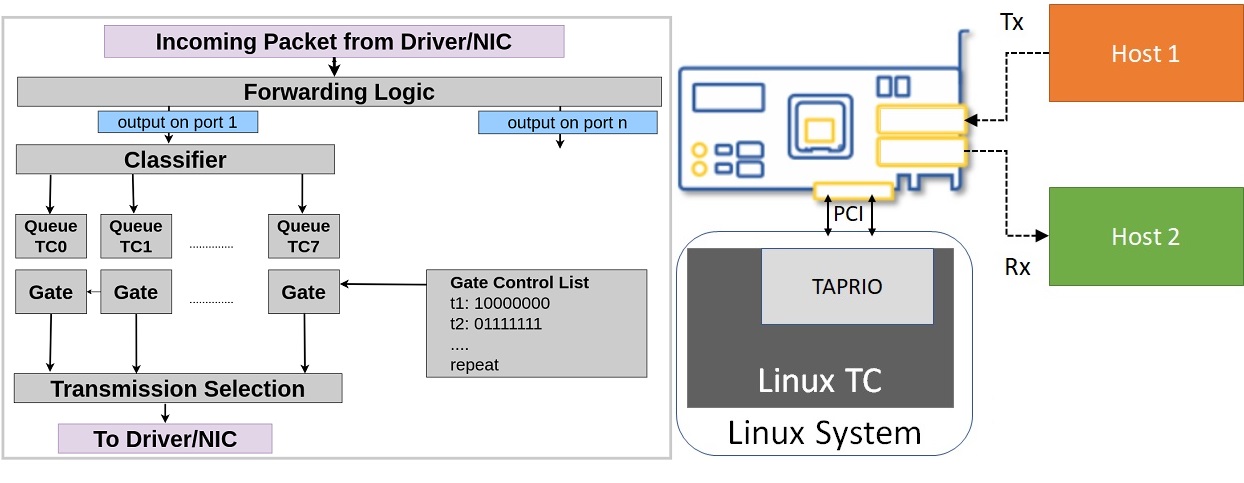

Time Aware Shaper (TAS) using LinuxTC on Netronome card Link to heading

TSN is the IEEE 802.1Q defined standard technology to provide deterministic messaging on standard Ethernet. It provides guarantees of delivery and minimized jitter using time scheduling for those real-time applications that require determinism. TAS is a feature specified in the IEEE 802.1Qbv standard that helps to guarantee bounded latency for time-critical frames in TSN by scheduling the transmission of frames within fixed intervals based on their priority.

Implementation of TAPRIO

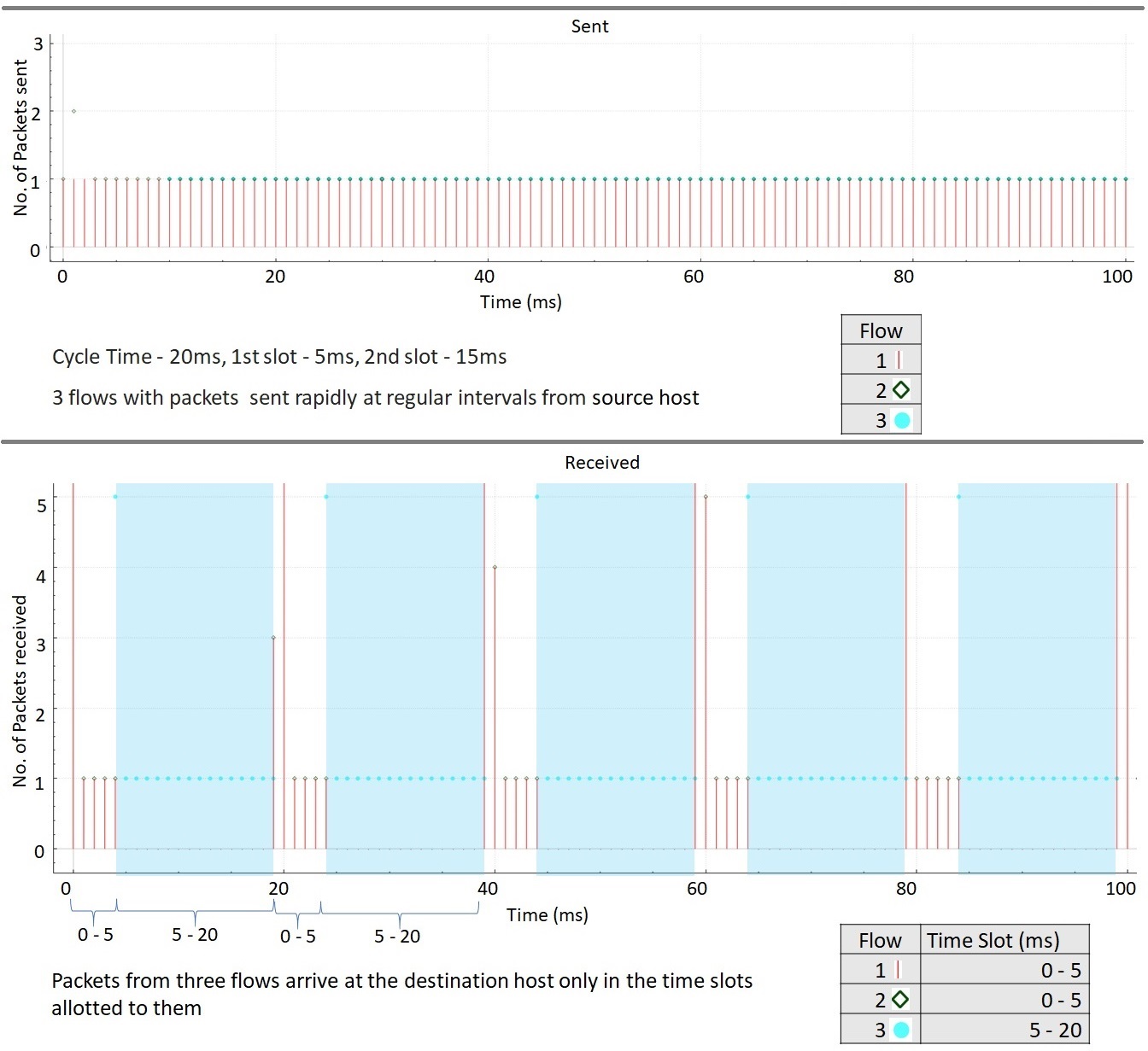

Results with cycle time of 20ms

Ongoing and future work: Link to heading

Related publications Link to heading

- EdgeP4: In-Network Edge Intelligence for a Tactile Cyber-Physical System Testbed Across Cities, IEEE INFOCOM CNERT 2024. Link

- Towards a TSN-DetNet Intercity Testbed for Tactile Cyber-Physical Systems, IEEE INFOCOM CNERT 2024. Link

- Enhancing Reliability of Scheduled Traffic in Time-Sensitive Networks using Frame Replication and Elimination, IEEE LANMAN 2023. Link

- μTAS: Design and implementation of Time Aware Shaper on SmartNICs to achieve bounded latency, prepint, 2023. Link